## Frequently Asked Questions B4655A FPGA Dynamic Probe for Xilinx

**Data Sheet**

This document addresses common questions whose answers are not found in the B4655A FPGA dynamic probe data sheet available at www.aqilent.com/find/FPGA

Agilent's FPGA dynamic probe provides greater realtime measurement productivity for logic analysis based validation of FPGAs and the surrounding system. The tool features:

- Increased visibility Traditional logic analyzer probes limit engineers to measuring signals at the periphery of the FPGA. With Agilent's FPGA dynamic probe, engineers are able to measure up to 128 internal FPGA signals for each external FPGA pin dedicated to debug.

- Faster probing changes Agilent's FPGA dynamic probe enables your design team to move probe points internal to the FPGA with a mouse click — without any design changes and without any changes to the timing of your design.

- Automatic setup of the logic analyzer The FPGA

dynamic probe maps internal signal names from your

FPGA design tool to your logic analyzer. The signalnaming capability of the Agilent FPGA probe eliminates

mistakes and saves you the time it would take to

manually set up signal and bus names and logic analyzer

connections, providing a significant advantage over logic

analyzers without this capability.

#### Q1 How do I create an ATC2 core?

Xilinx ChipScope Pro or EDK provides the capability to create an ATC2 core. You need Xilinx ChipScope Pro or EDK to create the ATC2 core and to merge it with your design. Using either of these tools, you can specify the parameters of the ATC2 core and specify which design signals go to the ATC2, making them available for real-time measurement.

#### Q2 How do I get an ATC2 core into my design?

Xilinx ChipScope Pro includes Core Inserter and Core Generator. Core Inserter puts the core into your FPGA design post synthesis. Agilent recommends using Core Inserter. If you use Xilinx Core Generator or EDK, the tool instantiates your parameterized ATC2 as a blackbox Verilog or VHDL unit. The synthesis tool puts the instantiated core into your design during the synthesis process.

### Q3 What synthesis tools can I use to get the ATC2 core into my design?

ATC2 cores produced by Xilinx Core Generator or EDK are compatible with:

- · Exemplar Leonardo Spectrum

- · Synopsys Design Compiler

- · Synopsys Design Compiler II

- · Synopsys FPGA Express

- · Synplicity Synplify

- · Xilinx XST

### **Q**4 Are there advantages to using Core Inserter versus Core Generator or EDK?

Yes. Core Inserter also produces a .cdc file. This is a small file listing the signal inputs to the ATC2 core. This file is used to automatically synchronize design signal names with logic analysis bus and signal names. Agilent recommends using Xilinx Core Inserter so you can take advantage of signal-name mapping. Xilinx has a stimulus core known as VIO. This core can only be created and placed in a design using Core Generator. For a single design that contains both a VIO core and an ATC2, Core Generator must be used.

Q5 Core Generator or EDK does not produce the .cdc file required for automated signal name entry in the logic analyzer. If I use Core Generator or EDK instead of Core Inserter is there a way for me to manually make my own .cdc file?

Yes. You have two different options.

- Run Core Generator or EDK and set the core parameters.

These tools will make a .cdc file that you can use as a template. Open the .cdc file template using a text editor.

Modify the bank input signal names so that they reflect the signal path name of the probed net.

- 2. The FPGA dynamic probe application reads core parameters via JTAG when the user initiates a JTAG communication session with the "Connect Cable" button. One of the parameters the logic analyzer reads is the number of signal banks, and the number of signals per bank. The logic analyzer application uses generic names for each signal when a .cdc file is not loaded. For example signal 0 is generically labeled as ATC 0 (Agilent Trace Core bit 0). On the logic analyzer, you can manually rename each ATC name with the signal names from your design. The FPGA dynamic probe application will remember name changes you made for each bank.

### **Q**6 How big is the ATC2 core? How many of my device resources does it take?

Each input signal adds roughly 1 slice to the size of the ATC2 core. The ATC2 cores have been designed to be as small as possible. For example, an ATC2 state core configured with 8 signal banks and 80 signals per bank consumes about 94 slices, or less than 1 percent of the resources on a Xilinx XCV2000 device.

The actual core size depends on parameters chosen such as:

- 1. Core type: state, state with pin compression or timing

- 2. Number of pins

- 3. Number of signal banks.

Xilinx recommends measuring core sizes in terms of flops and LUTs as this is what the place and route tools work with. A formula to determine LUT and flop resource utilization from the combination of the ATC2 core and ICON (JTAG controller) is available at <a href="http://www.agilent.com/find/fpga">http://www.agilent.com/find/fpga</a> or in the Xilinx Core Inserter tool.

## Q7 I already put my own MUXes in my FPGA design to better utilize debug pins. How is this solution better?

FPGA dynamic probe was designed to have minimal intrusion in both the design flow and the design itself. Here are the top areas where the FPGA dynamic probe solution will save you work and time, even if you already use your own MUXes.

- FPGA dynamic probe does not require you to modify your HDL code when using Core Inserter flow. Teams not using FPGA dynamic probe must modify HDL code to include MUXes.

- Control of which signals are presented for measurement is done from the logic analyzer in about a second (only 2 mouse clicks). Teams not using FPGA dynamic probe must design in special capability (such as changing register values) to change which signals are presented to IO pins for measurement.

- Because Xilinx Core Inserter puts pipelined ATC2 state cores in the design post-synthesis and before place and route, the inclusion of the ATC2 state core will be less intrusive than manual design of MUXes that do not incorporate pipelining.

- 4. FPGA dynamic probe enables graphical or auto pin mapping eliminating errors and time associated with the tedious manual process of determining and specifying how internal MUXes are connected to the logic analyzer and then typing each name into the logic analyzer.

- With FPGA dynamic probe, signal names are imported from the FPGA design tools and automatically updated in the logic analyzer each time the user selects a new signal bank to measure.

#### Q8 Why do I see flip flops in the timing core?

The path from the probed signal to the output pad is not registered in the timing core. This path has only a combinatorial mux connected to output pads. The flip flops in the timing core are used only for core control and status. An example of a core control signal is the bank mux select. These control and status flip flops are registered by the JTAG TCK clock, not a design clock. Therefore these flip flops are part of the low-speed circuit used by the logic analyzer to control and poll the core.

### Q9 Do I pay royalties for the use of the core?

No. ATC2 cores are distributed as part of Xilinx ChipScope Pro or EDK. There are no associated royalties.

### Q10 Should I leave the ATC2 core in my design after validation is complete?

This decision is up to you. Many designers prefer leaving debug cores in the design, as removing the cores from the design will change design timing. The core also can be useful for doing debug once units are in the field, if needed. The ATC2 core is by default "turned off," and it wakes when an Agilent logic analyzer communicates with it. This feature saves power when you leave the core in a finished design.

## Q11 When would I want to use an ATC2 state core (synchronous) versus a timing (asynchronous) core?

#### State cores:

- Provide most-accurate measurements for functional debug in one time domain

- · Register inputs to minimize fan out

- · Support time division multiplexing for 2X pin reduction

#### Timing cores:

- Are best for measurements across multiple time domains

- Run at fastest-possible speed of device, no registering of MUX inputs or outputs

- · Have minimal impact on design timing

## Q12 What effect does the core have on my design's timing? Does loading the ATC2 affect my signal routing?

The ATC2 core is a firm core. The core will not affect the synthesis of the design when you create and insert the core using Core Inserter. The inclusion of an ATC2 core in the design may affect the placement and routing of the overall FPGA design. In typical applications, the effect should be small. The effect on design timing will depend on how the core is configured (for example, the number of signals you choose per bank and the total number of banks) and the number of resources available on the particular FPGA device being used.

State core: The ATC2 state core includes a flop that registers data. The ATC2 core adds one additional load (flop) on each signal probed. This load will be factored into routing to meet user specified timing constraints. This flop helps the tools meet timing constraints for most types of designs.

Timing core: The ATC2 timing core adds a wire load for each signal probed. This wire load is a false path that is ignored during place and route of the design. Hence, the timing core has minimal-to-no effect on design timing. You can determine the skew between signals by viewing the delay file generated by the design tools to estimate this difference.

Once the ATC2 core (either state or timing core) is in the design, switching from signal bank to signal bank does not change design timing, as all connections have been already made.

#### Q13 What's the impact on FPGA performance?

The core will have some effect on performance, but it should not be significant. The effect on performance is directly related to timing constraints. The timing core is capable of running at the fastest internal FPGA speed of the device you are using. For the timing core, the sample rate on the logic analyzer will determine how often data is captured. For state cores, the maximum sample rate will be the lower of the speed of the FPGA time domain being measured or the maximum state speed of the logic analyzer. All supported logic analyzers have state speeds of 200 MHz and greater.

### **Q**14 How does the optional 2X pin compression technology work?

All signal inputs to the ATC2 state core are registered and clocked on the edge you specify. Internal to the core, the registered value of signal 1 is passed to the logic analyzer on the rising edge of the clock, and the value of signal 2 is passed to the logic analyzer on the falling edge of the clock. The logic analyzer uses a demultiplexing mode to decompress the information and preserve all triggering and analysis capabilities.

# Q15 If I have ATC2 signal banks with 64-bit width, how many pins and logic analyzer channels does it take with 2X pin compression turned on?

Simultaneous measurement of 64 signals requires 32 FPGA pins and 64 logic analysis channels. Only 32 of the logic analysis channels are physically connected to pins of the FPGA. The other 32 channels provide their acquisition memory and triggering resources for the measurement.

#### Q16 Can I simulate the ATC2 core?

No. Agilent guarantees that the ATC2 core meets specifications and characteristics listed in our data sheet. The core has been debugged and tested by Agilent.

### Q17 Can I use FPGA dynamic probe with multiple logic analyzers?

With option 011, the perpetual node locked license, the FPGA dynamic probe is licensed to the logic analyzer (1680 Series, 1690 Series, 16800 Series, 16900 Series, or U4154A). Multiple instances of the FPGA dynamic probe are provided so you can use a single license for all logic analysis modules in the system.

With option 012, the perpetual floating license, you have one instance of the FPGA dynamic probe that can be used by any 1680 Series, 1690 Series, 16800 Series, 16900 Series, or U4154A logic analyzer that has access to the license server.

#### Q18 Who do I contact if I'm having problems?

Xilinx provides ChipScope Pro and EDK expertise, including expertise on inserting the core into your design. Agilent's expertise is on the core and FPGA dynamic probe application. Agilent and Xilinx work together on issues that cross company boundaries.

### Q19 What if I didn't assign all of the signals of interest early when I created the core?

You can still use Xilinx FPGA editor to route new input signals to the ATC2 core. However, a new .cdc file is not produced, so you will need to update the new signal name on the logic analyzer. Alternatively, you can change input signals by recompiling the FPGA design with a new ATC2 core or new signal connections to the core.

# Q20 If I use FPGA editor, the signals being presented to the logic analyzer are now different from what the .cdc file specified. What can I do to reflect my design changes?

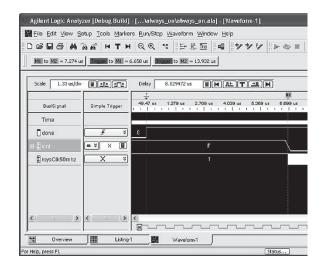

On the logic analyzer, you can manually rename whatever signal names you need to. In the FPGA dynamic probe application, simply activate the bank where the signal name change is needed. Then in the logic analyzer setup, listing, or waveform menu, modify the previous signal name with the new one you have routed out with FPGA Editor. The FPGA dynamic probe application will remember name changes you made for each bank signal.

## Q21 Can I use the FPGA dynamic probe application to download configuration bits into my Xilinx FPGA?

Yes.

### Q22 What Xilinx JTAG cables work with FPGA dynamic probe?

Xilinx Parallel III and IV MultiLINX cables and the platform USB cable. The cable makes a connection between the parallel or USB port on the logic analyzer and the JTAG pins on the FPGA being measured. Xilinx Platform Cable USB is supported on logic analyzers with Version 3.2 or higher software.

### Q23 Does the FPGA dynamic probe work if I have non-Xilinx devices on the scan chain?

Yes. The application can handle up to 256 devices in a scan chain. The devices can be Xilinx or non-Xilinx devices. When a non-Xilinx device is found, dynamic probe will ask for the JTAG IR length. This value is readily available from the chip manufacturer. The application saves this value and uses it when communicating with your scan chain.

When the application needs to talk to a selected Xilinx FPGA device, it puts all devices into bypass mode except for the selected device. BYPASS mode is a JTAG required function in which the device simply adds a flop delay between TDI data to TDO. When in bypass the data is ignored by the BYPASS-ed device and it operates as it normally does (for example a microprocessor keeps running user code). One thing to keep in mind is that Xilinx's parallel programmer hardware may not support driving 256 devices in one scan chain. In particular the TCK and TMS lines are heavily loaded when JTAG is configured as a chain. The reason is that the cable will drive TCK and TMS to all devices in a scan chain. For this reason you should consider buffering these signals on you board if you have more than six devices in a scan chain (simple rule of thumb). One other thing you can do if you have more than six devices or are simply having problems connecting to your FPGA is simply lower the JTAG TCK speed. With dynamic probe you can select from various speeds down to 200KHz as a TCK rate. By slowing down TCK you will increase the setup/hold margin for TMS on all devices and TDI on the first device.

#### 024 How does the test bank work?

The core contains test generation circuitry to stimulate the signal banks and output pins. With this active data running, the logic analyzer invokes the Eye Finder feature to automatically adjust for variances in path delays through the core to the acquisition system on the logic analyzer.

### Q25 Can I use the calibration feature with an ATC2 timing core?

No. Calibration works exclusively for ATC state analysis cores.

### Q26 Can I use a different clock on each bank or do I need a clock with each bank?

Timing cores do not have a clock, because information is sampled using the logic analyzer's internal clock. For state cores, the ATC2 core has a master clock that is used for all banks. Multiple ATC2 cores can be used for multiple clock domains.

### Q27 Can I put multiple ATC2 cores in a single device?

Yes. The FPGA dynamic probe application has been architected to support multiple cores in a single FPGA device. If the cores are state cores, each will need a clock from the design it is measuring.

### **Q**28 Can I map two cores onto a single physical probe?

Yes. For example the first ATC2 core with 16 output pins could be mapped to the outside of a mictor connector with its corresponding clock. A second ATC2 core with five output pins could be mapped to the even side of the same mictor connector. A separate logic analysis module is required to collect acquisition data for each core.

### Q29 Which Xilinx FPGAs are supported?

FPGA dynamic probe supports Xilinx Spartan-3, Virtex-II, Virtex-II Pro, Virtex-4, and Virtex-5 FPGAs.

### Q30 What triggering resources are available with the FPGA dynamic probe?

The full trigger resources of the Agilent logic analyzer being used are available.

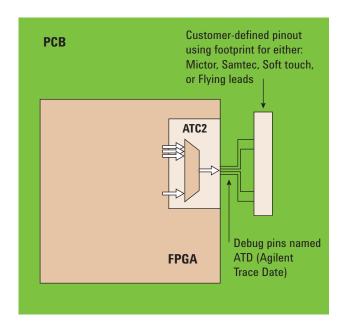

### Q31 What special pinouts are required by FPGA dynamic probe?

No special pinouts are required. The FPGA dynamic probe includes a graphical feature called pin mapping. This feature lets you visually tell the tool how the FPGA physical pins that carry the MUX output (ATD — Agilent Trace Data) are connected to the logic analyzer. If you are using a traditional probing connection, such as a Mictor or Samtec connector, or a soft touch probe, the graphic lets you specify the location of each ATC2 output and which logic analysis cable is connected to this probe.

### Q32 How does auto-setup (auto-pin mapping) work?

For ATC2 cores created with auto setup enabled, the FPGA dynamic probe application software will automatically determine correct pin mapping without manual intervention. Each pin of the ATC2 core, one at a time, will produce a unique stimulus pattern. The instrument looks for this unique pattern on any of its acquisition channels. When the instrument finds the pattern, it associates that instrument channel with the ATC2 output pin producing it. It then repeats the process for each of the remaining output pins eliminating the need to manually enter probe layout information. Auto-setup, is sometimes referred to as "plug & run" as it essentially lets a user plug in a logic analyzer cable and press the run button to take an acquisition.

# Q33 For ATC2 1x state cores how much latency exists from the point were a signal is probed to the time the logic in the analyzer acquires the state of the signal?

Latency is the time required for a signal to get through the flops and other logic.

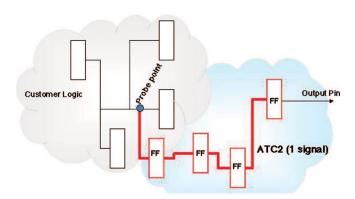

Using the Core Inserter method, the Xilinx place and route tools work with the constraint file originally specified. In order to minimize timing impacts that the addition of the ATC2 core to the user design might have, ATC2 state cores employ pipelining. The number of pipeline states is shown in the FPGA dynamic probe SW under properties. Multiple stages are advantageous as it allows the initial flop to be placed close to the signal being probed, and then uses additional flops to move across the chip to a pin. With pipelining, the length between flops is substantially less than if there was no pipelining. This minimizes timing impact.

With pipelining, ATC2 state core outputs will be presented to the logic analyzer (triggering and display) a few cycles apart from other non-ATC2 state core events the logic analyzer is simultaneously capturing.

For the ATC2 core latency is specific to the latency of the signals under test (customer signals). ATC2 state cores have a latency value that can be seen in the FPGA dynamic probe application software by selecting "properties". This latency value is the number of ATCK clocks that it takes for a probed signal to reach the output of the target FPGA. Latency will vary depending on which ATC2 core features were selected. For instance if auto-setup is removed, a 1x state core ends up with a 3 clock latency. However if auto-setup is added to the core it adds an additional clock cycle of latency.

The thick lines show the FF's and routes added by ATC2. Since there is a FF "in the fabric" in addition to one at the I/O, timing impact on your design is minimized.

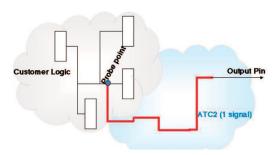

# Q34 For ATC2 timing cores how much latency exists from the point were a signal is probed to the time the logic in the analyzer acquires the signal?

The ATC2 does not account for the latency in a timing core. This can be obtained from the Xilinx delay report.

The thick lines show the routes added by ATC2 timing cores.

## Q35 When you select names of nets to probe in Xilinx Core Inserter, do you select from the post-synthesis net names or the original RTL names?

The signals names that Xilinx Core Inserter has access to are from the post-synthesis netlist. If there is an RTL name that you want to make sure does not get optimized out, you can use a command such as Synplicity's SYNKEEP to preserve RTL signals.

### Q36 Can I debug and probe at the RTL level, like Synplicity's Identify product?

No, the Xilinx Core Inserter currently works at the signal and bus level.

## Q37 Can I debug using FPGA dynamic probe with a design that has been instrumented using Synplicity's Identify product?

Not at the same time. Both tools require control of the JTAG scan chain and thus only one can be used at a time.

### Q38 Should I synthesize my FPGA design in one pass or hierarchically?

When selecting signal names for probing using Xilinx Core Inserter, the tool works best with a "flattened" design that was synthesized all at one time. If you have a hierarchical design, Core Inserter lets you select signals from the top level of the design.

### Q39 Can I feed an external clock in for a State measurement with a State core?

Yes, but this external clock would need to also drive the FPGA internal clock for the timebase being observed in order for the measurements to make sense. For example, you could use an external pulse generator, and feed it into the FPGA as a clock, and feed it into the clock input of the logic analyzer.

## Q40 Can I sequentially use ChipScope Pro ILA and FPGA dynamic probe (with the ATC2 core) on a design using the same JTAG cable?

Yes. There are two options. If you install ChipScope Pro on the Agilent logic analyzer this application will communicate via the JTAG cable connected to the parallel or USB port on the logic analyzer. The FPGA dynamic probe application also uses this same port and can "share" the cable. A user can toggle back and forth between the software application without making any cable or JTAG modifications as both applications use the same drivers for cable communication. The second option is to install ChipScope Pro on a standalone PC. In this case you can move the cable from the logic analyzer parallel or USB port to the equivalent port on the PC when you are using ChipScope Pro. Move the cable connection back to the logic analyzer parallel/USB port when you want to use the FPGA dynamic probe. (Note, in the second scenario the application which doesn't have direct cable access will not be able to take new measurements until the cable is connected.)

## Q41 Beginning with ChipScope 7.1i, there is a new ATC2 core parameter named "always-on." What does this do?

Always-on is a feature that enables the signals on bank 0 to be active after FPGA reconfiguration. This feature is exclusive for timing cores and is intended for debugging from reconfiguration without having to activate an initial bank via JTAG.

## Q42 For the ATC2 core parameter named "always-on" what should I consider when using it?

ATC2 core outputs will be enabled at reconfiguration and will remain active which will consume additional power. Outputs can only disabled through the FPGA dynamic probe via JTAG. For these reasons, use of the "always on" core parameter is typically used in applications where there is a need to debug from reconfiguration.

## Q43 For the ATC2 core parameter named "always-on" what should I consider when using it with a logic analyzer?

The correct order of events is critical when making a valid logic analysis measurement from FPGA reconfiguration. In addition to probing the ATC2 outputs, the logic analyzer will also need a separate signal connected to the DONE programming signal on the FPGA.

- a. Connect FPGA DONE pin signal to logic analyzer probe.

- b. On the logic analyzer, establish a connection to the ATC2 core using FPGA dynamic probe setup menu.

- c. Setup logic analyzer trigger for rising edge of DONE signal. This will cause the logic analyzer to trigger when the DONE signal goes high and capture information that occurs after the FPGA is configured. Additionally, you may want to set up a sequential trigger with additional sequences following finding a rising edge on DONE.

- d. Press the RUN button on the logic analyzer. The logic analyzer is now waiting to find the specified trigger condition. In this state, other logic analysis capabilities, such as FPGA dynamic probe configuration of the FPGA, are disabled.

- e. Configure FPGA using Xilinx IMPACT, ChipScope Pro, or some other means.

- f. The logic analyzer captures data after reconfiguration is complete.

### General questions on purchasing and installing ChipScope Pro tools

#### Q44 What is ChipScope Pro?

ChipScope Pro is the on-chip verification and debug tool for Xilinx FPGAs including:

- ILA core and ChipScope Pro Analyzer (not used in FPGA dynamic probe application)

- · Core Inserter

- · Core Generator

### **Q**45 What Xilinx FPGA devices do ChipScope Pro tools support?

ChipScope Pro tools support; Virtex-5, Virtex 4, Virtex, Virtex-E, Virtex-II, Virtex-II Pro, Virtex-II Pro X, Spartan-II, Spartan-IIE, and Spartan-3.

### Q46 Is ChipScope Pro sold as a time-based license agreement?

Yes, ChipScope Pro is sold under the standard Xilinx oneyear time-based license agreement.

### **Q**47 What do I get when I purchase ChipScope Pro tools?

You will receive a letter with a ChipScope Pro product ID and instructions on how to access ChipScope Pro tools including the ChipScope Pro Core Generator and Core Inserter, ChipScope Pro Analyzer, and ChipScope Pro soft cores (ILA, IBA, VIO), as well as the Agilent ATC2 core.

### Q48 How can I get the latest version of ChipScope Pro tools?

You can get the latest version of ChipScope Pro tools online at

http://www.xilinx.com/ise/verification/cs pro get.htm

### Q49 Is there an evaluation version of ChipScope Pro tools?

Yes, there is a full-featured 90-day evaluation version of ChipScope Pro tools that is available for download at http://www.xilinx.com/ise/verification/cs pro get.htm

### Questions on using ChipScope Protools

#### Q50 What is the ChipScope Pro Core Generator?

Similar to the ISE CoreGen tool, the ChipScope Pro Core Generator allows you to define parameters for ChipScope Pro cores, and generates synthesizable HDL that can be combined within your design.

#### Q51 What is the ChipScope Pro Core Inserter?

The ChipScope Pro Core Inserter allows you to add ChipScope Pro cores after the design has been synthesized by merging design netlists.

#### Q52 What is the ChipScope Pro Analyzer?

The ChipScope Pro Analyzer is the main interface that allows you to configure Xilinx FPGAs, find ChipScope Pro cores within a design, and set up and define trigger conditions. The ChipScope Pro Analyzer is similar to a logic analyzer, in that it allows you to view and interact with data captured for the purposes of debug and verification.

### Q53 What is ChipScope Pro ILA?

ChipScope Pro ILA (Integrated Logic Analyzer) allows you to view signals and nodes within the Xilinx FPGA design. Multiple trigger inputs, trigger sequencing and optional time stamping allow you to better utilize the available block RAM within your device under test. The ILA cores communicate via JTAG with the ChipScope Pro Analyzer software.

#### Q54 What is ChipScope Pro IBA?

ChipScope Pro IBA (Integrated Bus Analyzer) is the industry's first integrated bus analysis core. ChipScope Pro IBA is a CoreConnect-specific bus analyzer that allows you to capture and display transaction and signal activity between the PPC405 processor and IP components in the FPGA fabric.

### Questions on Xilinx and Agilent onchip debug solutions

#### Q55 What is the Agilent Xilinx relationship?

Teams within Agilent and Xilinx have worked closely together over the past several years to provide solutions for on-chip debug of Xilinx FPGAs. These solutions have become part of the Xilinx ChipScope Pro and FPGA Dynamic Probe tools.

## Q56 Are there any special compatibility issues between versions of Xilinx tools and Agilent logic analyzers or scopes?

Yes. New features are added regularly which require newer versions of instrument software that know about these features and how to work with them. Following is a chart with key ChipScope Pro/EDK versions and associated logic analyzer software versions.

| ChipScope Pro<br>Version | 1680, 1690, 16800, 16900<br>Series SW Version | Primary New Features                                                                                                                  |

|--------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 6.2i, 6.3i               | 2.5 or higher                                 | Mouse-click bank select, graphical pin mapping, .cdc signal name import                                                               |

| 6.2i, 6.3i               | 3.0 or higher                                 | Support for Virtex-4 devices, improved JTAG drivers, single-session multi-core support, user-definable naming                         |

| 7.1i                     | 3.2 or higher                                 | Plug & run (auto pin mapping), ATC2 "always on" option, ATC2 width = 64 banks, Platform Cable USB support, PRBS stimulus on test bank |

| 8.2i                     | 3.5 or higher                                 | Support for Virtex-5 devices and 16800 Series logic analyzers                                                                         |

| EDK Version 8.1i SP2     | 3.2 or higher                                 | EDK design flow support for ATC2 core                                                                                                 |

#### www.agilent.com

www.agilent.com/find/emailupdates

Get the latest information on the

products and applications you select.

#### www.axiestandard.org

AdvancedTCA® Extensions for Instrumentation and Test (AXIe) is an open standard that extends the AdvancedTCA® for general purpose and semiconductor test. Agilent is a founding member of the AXIe consortium.

#### www.lxistandard.org

LAN eXtensions for Instruments puts the power of Ethernet and the Web inside your test systems. Agilent is a founding member of the LXI consortium.

#### http://www.pxisa.org

PCI extensions for Instrumentation (PXI) modular instrumentation delivers a rugged, PC-based high-performance measurement and automation system.

#### **Agilent Channel Partners**

#### www.agilent.com/find/channelpartners

Get the best of both worlds: Agilent's measurement expertise and product breadth, combined with channel partner convenience.

Agilent Advantage Services is committed to your success throughout your equipment's lifetime. We share measurement and service expertise to help you create the products that change our world. To keep you competitive, we continually invest in tools and processes that speed up calibration and repair, reduce your cost of ownership, and move us ahead of your development curve.

www.agilent.com/find/advantageservices

www.agilent.com/quality

For more information on Agilent Technologies' products, applications or services, please contact your local Agilent office. The complete list is available at:

#### www.agilent.com/find/contactus

#### **Americas**

| Canada        | (877) 894 4414 |

|---------------|----------------|

| Brazil        | (11) 4197 3500 |

| Mexico        | 01800 5064 800 |

| United States | (800) 829 4444 |

#### **Asia Pacific**

| Australia          | 1 800 629 485  |

|--------------------|----------------|

| China              | 800 810 0189   |

| Hong Kong          | 800 938 693    |

| India              | 1 800 112 929  |

| Japan              | 0120 (421) 345 |

| Korea              | 080 769 0800   |

| Malaysia           | 1 800 888 848  |

| Singapore          | 1 800 375 8100 |

| Taiwan             | 0800 047 866   |

| Other AP Countries | (65) 375 8100  |

#### **Europe & Middle East**

| Belgium        | 32 (0) 2 404 93 40   |

|----------------|----------------------|

| Denmark        | 45 70 13 15 15       |

| Finland        | 358 (0) 10 855 2100  |

| France         | 0825 010 700*        |

|                | *0.125 €/minute      |

| Germany        | 49 (0) 7031 464 6333 |

| Ireland        | 1890 924 204         |

| Israel         | 972-3-9288-504/544   |

| Italy          | 39 02 92 60 8484     |

| Netherlands    | 31 (0) 20 547 2111   |

| Spain          | 34 (91) 631 3300     |

| Sweden         | 0200-88 22 55        |

| United Kingdom | 44 (0) 118 9276201   |

|                |                      |

For other unlisted Countries:

#### www.agilent.com/find/contactus

Revised: October 14, 2010

Product specifications and descriptions in this document subject to change without notice.

© Agilent Technologies, Inc. 2006, 2011 Printed in USA, March 23, 2011 5989-1170EN