For the Anritsu MP1900A BERT

## PCI Express® 5.0 Receiver Test Automation Software (GRL-PCIE5-RXA)

Quickly test your Design to the PCIe® 5.0 Base and CEM Specifications

- Automates PCle® 5.0 (32GT/s) Base and CEM Spec testing

- Perform Base and CEM Receiver Jitter Tolerance testing at the push of a button

- Perform PCle® TX and RX Link Equalization (Link EQ) tests at 32GT/s

- Reduce technical risk using an industry-accepted calibration methodology

- Achieve consistent results with rapid test execution

## **Product Overview**

The GRL PCI Express® and 5.0 Receiver Test Automation Software Suite (GRL-PCIE5-RXA) provides an automated, simple and efficient way to test your PCIe® 5.0 Host and Add-In Card designs using the Anritsu MP1900A with any Tektronix or Keysight Real-Time Oscilloscope.

GRL-PCIE5-RXA features two components that can be ordered separately or together: GRL-PCIE5-BASE-RXA for testing your PCIe® 5.0 Receiver to the Base (ASIC) Specification, and GRL-PCIE5-CEM-RXA for testing end products to the PCIe® 5.0 CEM (Card Electro-Mechanical) Specification. GRL-PCIE5-RXA provides a simple user interface to automate complex PCIe® testing, and significantly reduces equipment calibration and test time. The software runs on a Windows 7 or higher oscilloscope or PC.

BASE-RXA uses the industry-standard Seasim statistical data eye simulator to establish the calibrated test channel DDJ and arrive at the final stressed eye diagram. Receiver jitter tolerance and margin testing can then be performed on the device under test.

CEM-RXA uses the VNA method for channel measurement and SigTest for all other stressed eye impairments. Jitter Tolerance and Margin Testing is offered in both versions.

GRL-PCIE5-RXA also automates LTSSM training into loopback mode for RX Link EQ BER Measurement and TX Link EQ Tests.

## **Features**

- Automated calibration of signal impairments to achieve stressed Receiver Eye Height and Eye Width, in accordance with PCle® 5.0 Base & CEM Specification

- $\,\blacktriangleright\,$  Uses Industry Standard tools Seasim and SigTest for Stressed Signal Calibration

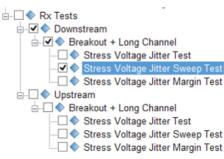

- > Automated Receiver Compliance and Jitter Tolerance and Marging testing

- > Using spec-defined or user-defined Jitter Frequency steps

- > Performs all CEM CTS Tests (Transmitter & Receiver) in single Software Framework

- > Simple setup, test execution, and reporting in PDF files

- > Fully configurable and customizable

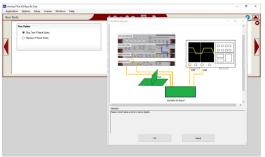

**Push-Button Automation**

**Fully Configurable**

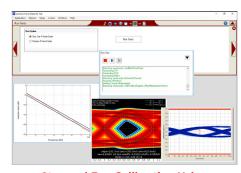

Stressed Eye Calibration Using Seasim and SigTest

Transmitter CEM Testing using GRL-PCIE34-TXP1

Silicon Valley, USA

Hsinchu & Taipei, Taiwan

Shanghai, China

Dongguan, China

Yokohama, Japan

Bangalore, India

Böblingen, Germany

**Singapore**

Penang, Malaysia

## **Application Specifications**

| Specification                      | PCI Express® Base Specification Revision 5.0, Version 1.0 PCI Express® CEM Specification Revision 5.0, draft (contact GRL for details)                                                                                     |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Rates                         | 32 GT/s                                                                                                                                                                                                                    |

| Stressed Eye<br>Calibration Method | For Base: Seasim for Insertion Loss, Seasim & SigTest for final eye calibration using Fixed or Variable ISI Solutions For CEM: SigTest using PCIe® CEM CLB/CBB Fixtures                                                    |

| Supported Tests from PCIe® 5.0     | GRL-PCIE5-BASE-RXA: Rx Jitter Tolerance & Margin Testing<br>GRL-PCIE5-CEM-RXA: Rx Jitter Tolerance & Margin Testing, Initial Tx EQ,<br>Lane Margining, Link EQ Response, and Receiver Link EQ for Host and<br>Add-In Cards |

## **Ordering information**

For a formal quote & pricing information, contact info@graniteriverlabs.com, or your Anritsu sales representative.

| Model Number       | Description                                                                                                                                                                                         |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GRL-PCIE5-BASE-RXA | GRL PCle® 5.0 (32GT/s) Base Specification Receiver Test                                                                                                                                             |

| GRL-PCIE5-CEM-RXA  | GRL PCIe® 5.0 (32GT/s) CEM Specification Receiver Test SW<br>Rx Jitter Tolerance & Margin Testing, Tx Link EQ, Lane Margining, Link EQ<br>Response, and Receiver Link EQ for Hosts and Add-In Cards |

| GRL-PCIE5-RXA      | GRL PCle® 5.0 (32GT/s) Base & CEM Specification Receiver Test SW Bundle                                                                                                                             |

| GRL-PCIE5-XXX-RXA  | FLT Adds floating license through USB Dongle                                                                                                                                                        |

# GRANITE RIVER LABS

#### **World Wide Headquarters**

#### Granite River Labs

3500 Thomas Road, Suite A Santa Clara, CA 95054 USA +1 (408) 627-7608 info@graniteriverlabs.com www.graniteriverlabs.com

## **About Granite River Labs**

The world's leading Engineering Services and Test Automation Solutions firm for connectivity, GRL helps engineers solve tough design and validation challenges. GRL began in 2010 with a vision to provide affordable test services to help hardware developers implement digital interface technologies as they become faster, more complex, and more challenging to test. Today, GRL has worked with hundreds of companies from our worldwide test facilities and R&D centers.

For additional information or questions regarding Granite River Labs, including quotes, product demonstrartions, software and technical assistance, please contact us at info@graniteriverlabs.com.

© Granite River Labs Asia Pacific Pte. Ltd. All rights reserved. All trademarks used in this document are the property of their respective owners. Product specifications and descriptions in this document subject to change without notice. Contact your sales consultant for the latest information.

GRL-PCIE5-RXA. Published Aug 2019.