#### **SPECIFICATIONS**

# PXIe-6570

#### 100 MVector/s PXI Digital Pattern Instrument

These specifications apply to the PXIe-6570. When using the PXIe-6570 in the Semiconductor Test System, refer to the *Semiconductor Test System Specifications*.

## Contents

| Definitions                         | 2  |

|-------------------------------------|----|

| Conditions                          | 2  |

| General                             | 2  |

| Timing                              | 3  |

| Vector Timing.                      | 3  |

| Clocking                            | 3  |

| Drive and Compare Formats           | 4  |

| Pin Data States                     |    |

| Edge Timing                         | 6  |

| Driver, Comparator, Load            | 7  |

| Driver                              |    |

| Comparator                          | 8  |

| Active Load                         |    |

| PPMU                                | 8  |

| PPMU Force Voltage                  | 8  |

| PPMU Measure Voltage                | 9  |

| PPMU Force Current.                 | 9  |

| PPMU Measure Current                | 11 |

| PPMU Programmable Aperture Time     | 12 |

| Pattern Control.                    | 13 |

| Opcodes                             | 13 |

| Pipeline Latencies                  | 14 |

| Source and Capture                  | 14 |

| Independent Clock Generators        | 15 |

| Frequency Measurements              | 15 |

| Calculating Frequency Counter Error | 15 |

| Calibration Interval                |    |

| Physical Characteristics            | 16 |

| Power Requirements                  | 17 |

### **Definitions**

Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Warranted specifications account for measurement uncertainties, temperature drift, and aging. Warranted specifications are ensured by design or verified during production and calibration.

The following characteristic specifications describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.

- Typical specifications describe the performance met by a majority of models.

- Nominal specifications describe an attribute that is based on design, conformance testing, or supplemental testing.

Specifications are *Nominal* unless otherwise noted.

### **Conditions**

Specifications are valid under the following conditions unless otherwise noted.

- Operating temperature of 0 °C to 45 °C

- Operating temperature within  $\pm 5$  °C of the last self-calibration temperature

- Recommended calibration interval of 1 year. The PXIe-6570 will not meet specifications unless operated within the recommended calibration interval.

- DUT Ground Sense (DGS) same potential as the Ground (GND) pins

**Note** The DGS feature is only available on PXIe-6570 module revisions 158234C-xxL or later.

- Chassis fans set to the highest setting if the PXI Express chassis has multiple fan speed settings

- 30-minute warmup time before operation

**Note** When the pin electronics on the PXIe-6570 are in the disconnect state, some I/O protection and sensing circuitry remain connected. Do not subject the PXIe-6570 to voltages beyond the supported measurement range.

#### General

| Channel count                       | 32 |

|-------------------------------------|----|

| Multi-site resources per instrument |    |

| NI-Digital 16.0                     | 4  |

| NI-Digital 17.0 and later           | 8  |

| System channel count <sup>1</sup>        | 256                      |

|------------------------------------------|--------------------------|

| Large Vector Memory (LVM)                | 128M vectors             |

| History RAM (HRAM)                       |                          |

| NI-Digital 17.5 and earlier              | 1,023 cycles             |

| NI-Digital 18.0 and later                | (8,192/N sites)-1 cycles |

| Maximum allowable offset (DGS minus GND) | ±300 mV                  |

| Supported measurement range <sup>2</sup> | -2 V to 7 V <sup>3</sup> |

## **Timing**

## **Vector Timing**

| Maximum vector rate      | 100 MHz                                  |

|--------------------------|------------------------------------------|

| Vector period range      | 10 ns to 40 μs (100 MHz to 25 kHz)       |

| Vector period resolution | 38 fs                                    |

| Timing control           |                                          |

| Vector period            | Vector-by-vector on the fly              |

| Edge timing              | Per channel, vector-by-vector on the fly |

| Drive formats            | Per channel, vector-by-vector on the fly |

|                          |                                          |

## Clocking

| Master clock source     | PXIe_CLK100 <sup>4</sup>           |  |

|-------------------------|------------------------------------|--|

| Sequencer clock domains | \ 1 1                              |  |

|                         | a single instrument not supported) |  |

<sup>&</sup>lt;sup>1</sup> The system channel count is the maximum number of channels available when using multiple PXIe-6570 instruments in a single chassis as a digital subsystem. Some functionality described in this document requires that a PXIe-6674T synchronization module be used in conjunction with each digital subsystem.

<sup>&</sup>lt;sup>2</sup> If the total voltage sourced or driven on any pin relative to GND exceeds the supported measurement range, instrument performance may be degraded.

<sup>&</sup>lt;sup>3</sup> Voltages > 6 V require the Extended Voltage Range mode of operation.

<sup>&</sup>lt;sup>4</sup> Sourced from chassis 100 MHz backplane reference clock, external 10 MHz reference, or PXIe-6674T.

### **Drive and Compare Formats**

| Drive formats <sup>5</sup>    |                                                          |

|-------------------------------|----------------------------------------------------------|

| 100 MHz maximum vector rate   | Non-Return (NR), Return to Low (RL), Return to High (RH) |

| 50 MHz maximum vector rate    | Surround by Complement (SBC) <sup>6</sup>                |

| Compare formats               | Edge strobe                                              |

| Edge Multipliers <sup>5</sup> |                                                          |

| NI-Digital 17.5 and earlier   | 1x                                                       |

| NI-Digital 18.0 and later     | 1x, 2x                                                   |

| MI-Digital 16.0 and later     | 11, 41                                                   |

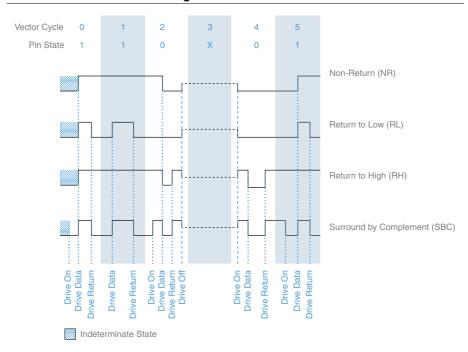

Figure 1. Drive Formats

When using NI-Digital 18.0 and later, the maximum vector rate for patterns may be limited by the pulse width requirements, which may not allow all formats and edge multipliers to be used up to the fastest vector rate.

<sup>&</sup>lt;sup>6</sup> The SBC format is not supported within the 2x edge multiplier mode.

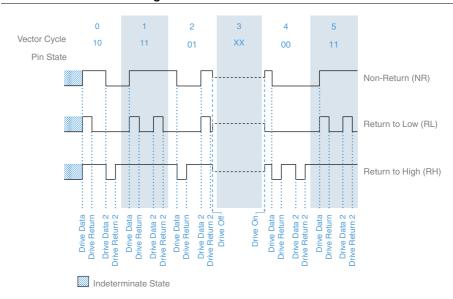

Figure 2. 2x Mode Drive Formats

#### Pin Data States

#### Pin States

- 0 Drive zero.

- 1 Drive one.

- L Compare low.

- H Compare high.

- X Do not drive; mask compare.

- M Compare midband, not high or low.

- V Compare high or low, not midband; store results from capture functionality if configured.

- D Drive data from source functionality if configured.

- E Expect data from source functionality if configured.<sup>7</sup>

- — Repeat previous cycle. Do not use a dash (-) for the pin state on the first vector of a pattern file unless the file is used only as a target of a jump or call operation.

**Note** Termination mode settings affect the termination applied to all non-driving pin states. Non-drive states include L, H, M, V, X, E, and potentially -. Refer to the Programmable input termination mode specification for more information.

<sup>&</sup>lt;sup>7</sup> This functionality requires NI-Digital 18.0 or later.

## **Edge Timing**

### **Edge Types**

Drive edges

| 4; drive on, drive data, drive return                                             |

|-----------------------------------------------------------------------------------|

| 6; drive on, drive data, drive return,<br>drive data 2, drive return 2, drive off |

|                                                                                   |

| 1; strobe                                                                         |

| 2; strobe, strobe 2                                                               |

| 31                                                                                |

|                                                                                   |

|                                                                                   |

| Start of vector period (0 ns)                                                     |

| 5 vector periods or 40 $\mu$ s, whichever is smaller                              |

|                                                                                   |

|                                                                                   |

| 5 ns                                                                              |

| 3.75 ns                                                                           |

| 5 ns                                                                              |

| 5 ns                                                                              |

| 39.0625 ps                                                                        |

|                                                                                   |

|                                                                                   |

±500 ps, warranted

±500 ps, warranted

Bit rate  $\leq 200$  Mbps:  $\pm 500$  ps, typical

Bit rate  $\leq$  266 Mbps:  $\pm$ 600 ps, typical

NI-Digital 17.5 and earlier

Edge Multiplier = 1x

NI-Digital 18.0 and later

Edge Multiplier = 1x

Edge Multiplier = 2x

Edge Multiplier = 2x

<sup>8 31</sup> time sets can be configured. One additional time set, represented by a -, repeats the previous time set.

<sup>9</sup> For specifications in a Semiconductor Test System, refer to the Semiconductor Test System Specifications.

| Eage placement accuracy. Compare | Edge 1 | olacement | accuracy: | Compare <sup>9</sup> |

|----------------------------------|--------|-----------|-----------|----------------------|

|----------------------------------|--------|-----------|-----------|----------------------|

| NI-Digital 17.5 and earlier          |                                                 |

|--------------------------------------|-------------------------------------------------|

| Edge Multiplier = $1x$               | ±500 ps, warranted                              |

| NI-Digital 18.0 and later            |                                                 |

| Edge Multiplier = $1x$               | ±500 ps, warranted                              |

| Edge Multiplier = $2x$               | Bit rate $\leq 100$ Mbps: $\pm 500$ ps, typical |

| Edge Multiplier = $2x$               | Bit rate $\leq 133$ Mbps: $\pm 700$ ps, typical |

| Overall timing accuracy <sup>9</sup> |                                                 |

| NI-Digital 17.5 and earlier          |                                                 |

| Edge Multiplier = $1x$               | ±1.5 ns, warranted                              |

| NI-Digital 18.0 and later            |                                                 |

| Edge Multiplier = $1x$               | ±1.5 ns, warranted                              |

| Edge Multiplier = $2x$               | Bit rate $\leq 200$ Mbps: $\pm 1.5$ ns, typical |

| Edge Multiplier = $2x$               | Bit rate $\leq$ 266 Mbps: $\pm$ 1.8 ns, typical |

| TDR deskew adjustment resolution     | 39.0625 ps                                      |

|                                      |                                                 |

# Driver, Comparator, Load

## Driver

| Signal type                                     | Single-ended, referenced to the DGS pin when connected. Otherwise referenced to GND. |

|-------------------------------------------------|--------------------------------------------------------------------------------------|

| Programmable levels                             | V <sub>IH</sub> , V <sub>IL</sub> , V <sub>TERM</sub>                                |

| Voltage levels                                  |                                                                                      |

| Range ( $V_{IH}$ , $V_{IL}$ , $V_{TERM}$ )      | -2 V to 6 V                                                                          |

| Minimum swing ( $V_{IH}$ minus $V_{IL}$ )       | $400 \text{ mV}$ , into a $1 \text{ M}\Omega$ load                                   |

| Resolution ( $V_{IH}$ , $V_{IL}$ , $V_{TERM}$ ) | 122 μV                                                                               |

| Accuracy $(V_{IH}, V_{IL}, V_{TERM})$           | $\pm 15$ mV, 1 M $\Omega$ load, warranted                                            |

| Maximum DC drive current                        | ±32 mA                                                                               |

| Output impedance                                | 50 Ω                                                                                 |

| Rise/fall time, 20% to 80%                      | 1.2 ns, up to 5 V                                                                    |

# Comparator

| Signal type                          | Single-ended, referenced to the DGS pin when connected. Otherwise referenced to GND. |

|--------------------------------------|--------------------------------------------------------------------------------------|

| Programmable levels                  | $V_{OH}, V_{OL}$                                                                     |

| Voltage levels                       |                                                                                      |

| Range ( $V_{OH}, V_{OL}$ )           | -2 V to 6 V                                                                          |

| Resolution ( $V_{OH}$ , $V_{OL}$ )   | 122 μV                                                                               |

| Accuracy $(V_{OH}, V_{OL})$          | $\pm 25$ mV, from -1.5 V to 5.8 V, warranted                                         |

| Programmable input termination modes | High Z, 50 $\Omega$ to $V_{TERM}$ , Active Load                                      |

| Leakage current                      | <15 nA, in the High Z termination mode                                               |

### **Active Load**

| Programmable levels                     | $I_{OH}, I_{OL}$                    |

|-----------------------------------------|-------------------------------------|

| Commutating voltage (V <sub>COM</sub> ) |                                     |

| Range                                   | -2 V to 6 V                         |

| Resolution                              | 122 μV                              |

| Current levels                          |                                     |

| Range                                   | 1.5 mA to 24 mA                     |

| Resolution                              | 488 nA                              |

| Accuracy                                | 1 mA, 3 V over/under drive, typical |

# **PPMU**

# PPMU Force Voltage

| Signal type | Single-ended, referenced to the DGS pin when |

|-------------|----------------------------------------------|

|             | connected. Otherwise referenced to GND.      |

#### Voltage levels

| -2 V to 6 V                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------|

| -2 V to 6 V<br>6 V to 7 V in Extended Voltage Range <sup>10</sup>                                                        |

| 122 μV                                                                                                                   |

|                                                                                                                          |

| $\pm 15$ mV, 1 M $\Omega$ load, from -2 V to 6 V, warranted                                                              |

| $\pm 15$ mV, 1 MΩ load, from -2 V to 6 V,<br>warranted<br>$\pm 50$ mV, 1 MΩ load, from 6 V to 7 V, typical <sup>10</sup> |

|                                                                                                                          |

## PPMU Measure Voltage

| Signal type    | Single-ended, referenced to the DGS pin when connected. Otherwise referenced to GND. |

|----------------|--------------------------------------------------------------------------------------|

| Voltage levels |                                                                                      |

| Range          | -2 V to 6 V                                                                          |

| Resolution     | 228 μV                                                                               |

| Accuracy       | ±5 mV, warranted                                                                     |

### **PPMU Force Current**

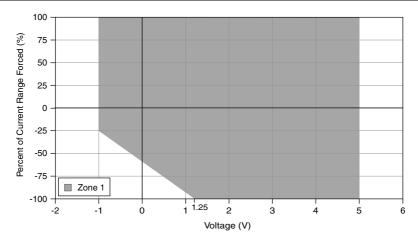

Table 1. PPMU Force Current Accuracy

| Range   | Resolution | Accuracy                                                           |

|---------|------------|--------------------------------------------------------------------|

| ±2 μA   | 60 pA      | ±1% of range for Zone 1 of <i>Figure 3</i> . on page 10, warranted |

| ±32 μΑ  | 980 pA     |                                                                    |

| ±128 μΑ | 3.9 nA     |                                                                    |

| ±2 mA   | 60 nA      |                                                                    |

| ±32 mA  | 980 nA     |                                                                    |

<sup>10</sup> The Extended Voltage Range is an unwarranted mode of operation that allows the PMU to force voltages between 6 V and 7 V for applications that can tolerate more error than the normal force voltage accuracy.

Figure 3. Warranted Current Accuracy Zone for PPMU Force Current

**Note** The boundaries of Zone 1 are inclusive of that zone. The area outside of Zone 1 does not have a warranted spec for PPMU force current accuracy.

#### How to Calculate PPMU Force Current Accuracy

- 1. Specify the desired forced current.

- 2. Based on the desired forced current, select an appropriate current range from Table 1.

- 3. Divide the desired forced current from step 1 by the current range from step 2 and multiply by 100 to calculate the Percent of Current Range Forced.

- Based on the impedance of the load, calculate the voltage required to force the desired 4. current from step 1. Use the following equation: Voltage Required = Desired Current \* Load Impedance.

- Using Figure 2, locate the zone in which the Percent of Current Range Forced calculated 5. in step 3 intersects with the Voltage calculated in step 4. If the intersection is outside of Zone 1, then there are no warranted specs. To get warranted specs, the current range and/or forced current must be adjusted until the intersection is in Zone 1.

- Based on the zone found in step 5, use Table 1 to calculate the accuracy of the forced current.

| PPMU voltage clamps |                  |  |

|---------------------|------------------|--|

| Range               | -2 V to 6 V      |  |

| Resolution          | 122 μV           |  |

| Accuracy            | ±100 mV, typical |  |

#### **PPMU Measure Current**

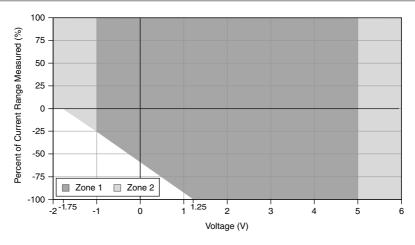

Table 2. PPMU Measure Current Accuracy

| Range   | Resolution | Accuracy                                                                   |

|---------|------------|----------------------------------------------------------------------------|

| ±2 μA   | 460 pA     | ±1% of range for Zone 1 of <i>Figure 4</i> . on page 11, warranted         |

| ±32 μΑ  | 7.3 nA     | $\pm 1.5\%$ of range for Zone 2 of <i>Figure 4</i> . on page 11, warranted |

| ±128 μΑ | 30 nA      |                                                                            |

| ±2 mA   | 460 nA     |                                                                            |

| ±32 mA  | 7.3 μΑ     |                                                                            |

Figure 4. Warranted Current Accuracy Zones for PPMU Measure Current

**Note** The boundaries of Zone 1 are inclusive of that zone. All other boundaries are inclusive of Zone 2. The area outside of Zone 1 and Zone 2 does not have a warranted spec for PPMU measure current accuracy.

#### How to Calculate PPMU Measure Current Accuracy

- 1. Specify the desired measured current.

- 2. Based on the desired measured current, select an appropriate current range from Table 2.

- 3. Divide the desired measured current from step 1 by the current range from step 2 and multiply by 100 to calculate the Percent of Current Range Measured.

- 4. If forcing voltage and then measuring current, Voltage in Figure 3 is equal to the forced voltage. If forcing current and then measuring current, Voltage in Figure 3 is equal to the

- voltage required to force the desired current based on the impedance of the load. Use the following equation: Voltage Required = Desired Current \* Load Impedance.

- Using Figure 3, locate the zone in which the Percent of Current Range Measured calculated in step 3 intersects with the Voltage calculated in step 4. If the intersection is outside of Zone 1 or Zone 2, then there are no warranted specs. To get warranted specs, the current range and forced current or forced voltage must be adjusted until the intersection is in Zone 1 or Zone 2.

- Based on the zone found in step 5, use Table 2 to calculate the accuracy of the measured current.

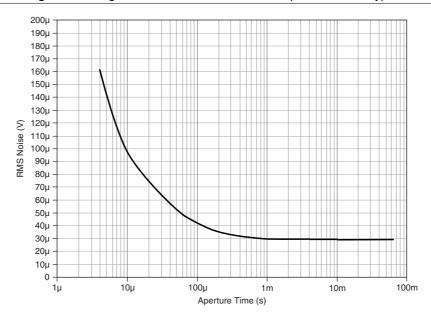

## PPMU Programmable Aperture Time

| Aperture time |       |  |

|---------------|-------|--|

| Minimum       | 4 μs  |  |

| Maximum       | 65 ms |  |

| Resolution    | 4 μs  |  |

Figure 5. Voltage Measurement Noise for Given Aperture Times, Typical

## Pattern Control

## **Opcodes**

Refer to the following table for supported opcodes. Using matched and failed opcode parameters with multiple PXIe-6570 instruments requires the PXIe-6674T synchronization module. Other uses of flow-control opcodes with multiple PXIe-6570 instruments only require NI-TCLK synchronization.

| Category                      | Supported Opcodes |

|-------------------------------|-------------------|

| Flow Control                  | • repeat          |

|                               | • jump            |

|                               | • jump_if         |

|                               | • set_loop        |

|                               | • end_loop        |

|                               | • exit_loop       |

|                               | • exit_loop_if    |

|                               | • call            |

|                               | • return          |

|                               | • keep_alive      |

|                               | • match           |

|                               | • halt            |

| Sequencer Flags and Registers | • set_seqflag     |

|                               | • clear_seqflag   |

|                               | • write_reg       |

| Category                   | Supported Opcodes  |

|----------------------------|--------------------|

| Signal                     | • set_signal       |

|                            | • pulse_signal     |

|                            | • clear_signal     |

| Digital Source and Capture | • capture_start    |

|                            | • capture          |

|                            | • capture_stop     |

|                            | • source_start     |

|                            | • source           |

|                            | • source_d_replace |

Note The source\_d\_replace opcode is only available with NI-Digital 18.0 or later

### **Pipeline Latencies**

Minimum delay between source\_start 3 μs

opcode and the first source opcode or

subsequent source\_start opcode

Matched and failed condition pipeline 80 cycles

latency

## Source and Capture

| Digital Source <sup>11</sup>  |                                                |

|-------------------------------|------------------------------------------------|

| Operation modes               | Serial and parallel; broadcast and site-unique |

| Source memory size            | 32 MB (256 Mbit) total                         |

| Maximum waveforms             | 512                                            |

| Digital Capture <sup>11</sup> |                                                |

| Operation modes               | Serial and parallel; site-unique               |

| Capture memory size           | 1 million samples                              |

| Maximum waveforms             | 512                                            |

To learn how to calculate achievable data rates for Digital Source or Digital Capture, visit ni.com/ info and enter the info code DigitalSourceCapture to access the Calculating Digital Source Rate tutorial or the Calculating Digital Capture Rate tutorial.

## Independent Clock Generators

**Note** This functionality requires NI-Digital 18.0 or later.

| Number of Clock Generators | 32 (one per pin)                                   |

|----------------------------|----------------------------------------------------|

| Clock Period Range         | 6.25 ns to 40 us (160 MHz to 25 kHz) <sup>12</sup> |

| Clock Period Resolution    | 38 fs                                              |

## Frequency Measurements

Note This functionality requires NI-Digital 17.0 or later.

| Frequency counter measure fre | quency                                       |

|-------------------------------|----------------------------------------------|

| Range                         | 5 kHz to 200 MHz, 2.5 ns minimum pulse width |

| Accuracy                      | See Calculating Frequency Counter Error      |

## Calculating Frequency Counter Error

Use the following equation to calculate the frequency counter error (ppm).

$$\left(\frac{TB_{err}}{\left(1-TB_{err}\right)} + \frac{20ns}{(MeasurementTime-UnknownClockPeriod)}\right) * 1,000,000$$

where

MeasurementTime is the time, in seconds, over which the frequency counter measurement is configured to run

UnknownClockPeriod is the time, in seconds, of the period of the signal being measured TB<sub>err</sub> is the error of the Clk100 timebase

Refer to the following table for a few examples of common Clk100 timebase accuracies.

Table 3. TBerr

| PXI Express Hardware Specification<br>Revision 1.0 | PXIe-1085 Chassis | PXIe-6674T Override |

|----------------------------------------------------|-------------------|---------------------|

| 100 μ (100 ppm)                                    | 25 μ (25 ppm)     | 80 n (80 ppb)       |

<sup>12</sup> Clocks with a period < 7.5 ns will have a non-50% duty cycle.

#### **Example 1: Calculating Error with a PXIe-1085 Chassis**

Calculate the error of performing a frequency measurement of a 10 MHz clock (100 ns period) with a 1 ms measurement time using the PXIe-Clk100 provided by the PXIe-1085 chassis as the timebase

Solution

$$\left(\frac{25\mu}{(1-25\mu)} + \frac{20ns}{(1ms-100ns)}\right) * 1,000,000$$

$$= 45ppm$$

#### Example 2: Calculating Error when Overriding with the PXIe-6674T

Calculate the error if you override the PXIe-Clk100 timebase with the PXIe-6674T and increase the measurement time to 10 ms.

Solution

$$\left(\frac{80n}{(1-80n)} + \frac{20ns}{(10ms-100ns)}\right) * 1,000,000$$

$$= 2ppm$$

### Calibration Interval

## **Physical Characteristics**

| PXIe slots | 2                                                        |

|------------|----------------------------------------------------------|

| Dimensions | 131 mm $\times$ 42 mm $\times$ 214 mm (5.16 in. $\times$ |

|            | 1.65 in. × 8.43 in.)                                     |

| Weight     | 920 g (32.45 oz.)                                        |

# **Power Requirements**

The PXIe-6570 draws current from a combination of the 3.3 V and 12 V power rails. The maximum current drawn from each of these rails can vary depending on the PXIe-6570 mode of operation. The total power consumption will not exceed the input power specification.

| Input power  | 68 W  |  |

|--------------|-------|--|

| Current Draw |       |  |

| 3.3 V        | 4.4 A |  |

| 12 V         | 4.7 A |  |

Information is subject to change without notice. Refer to the *NI Trademarks and Logo Guidelines* at ni.com/trademarks for information on NI trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering NI products/technology, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents. You can find information about end-user license agreements (EULAs) and third-party legal notice in the readmer file for your NI product. Refer to the *Export Compliance Information* at ni.com/legal/export-compliance for the NI global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data. NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS. U.S. Government Customers: The data contained in this manual was developed at private expense and is subject to the applicable limited rights and restricted data rights as set forth in FAR 52.227-14, DFAR 252.227-7014, and DFAR 252.227-7015.

© 2015—2018 National Instruments. All rights reserved.