# Keysight Technologies 15431A Filter Set for 81150A

Generates Random Jitter Profile for Testing PCI Express® 2.0 Receivers

## PCI Express® 2.0 Physical Layer Testing

Increasing speed rate for PCI Express Generation 2 is driving design to new dimensions. Validating and testing of PCI Express devices at the physical layer is getting more and more challenging for today's engineers.

PCIe ® 2.0 doubles the data rate from 2.5 Gbit/s to 5 GBit/s, improves point-to-point data transfer protocol and becomes more tolerant of jitter. Therefore the jitter tolerance and transfer measurement become more important.

## Keysight's Offering

Keysight Technologies, Inc. offers serial and multi-lane RX testing.

### J-BERT N4903A High-Performance Serial BERT

allows single-lane characterization of jitter tolerance from the device's input, checks compliance by emulating jitter conditions and has built-in mask tests and eye analysis tools to evaluate the PCIe 2.0 design.

# ParBERT 81250A High-Performance Parallel Bit Error Ratio Tester

is a modular BERT platform for clock, data generation and data analysis that allows configuring of a solution with up to 64 output and input channels. Its jitter modulation capability via the delay control input, together with the PCIe multi-lane receiver compliance test suite make it an automated and highly accurate tool for multi-lane PCI Express receiver tolerance compliance and characterization testing. The PCIe 2.0 specification defines a dedicated random jitter profile. The required control voltage for ParBERT's delay control input can be generated by the Keysight 81150A, a pulse function arbitrary noise generator.

### The 81150A Pulse Function Arbitrary Noise Generator

provides white Gaussian noise with a selectable crest factor up to 7 ( $V_{peak} / V_{RMS}$ ) or 14 ( $V_{peak peak} / V_{RMS}$ ). The long repetition rate of 26 days ensures real random noise. After 26 days the noise pattern starts from the beginning. The Keysight 15431A noise filter is an instrument accessory that is intended to be used for jitter measurements on PCle 2.0 with the 81150A as noise source and the N4903A or the 81250A as jitter tolerance tester. The proper jitter spectrum is achieved by filtering the white noise with a PCle 2.0-specific filter. The filter can serve two topologies: data driven and common clock

Table 1. Two different clocking architectures

#### Two different clocking architectures

#### Common reference clock

- RX sampling on (multiplied) ref clk

- RX w /DLL only (no CDR/PLL)

- SSC off: no phase error induced

- SSC on:

- Small error (femtoseconds) due to path delay difference (!) but

- Significant residual phase error due to potentially different transfer functions (BW and peaking) of TX and RX clock multiplying PLLs (CMU)

#### Data clocked (embedded clock)

- Receiver with PLL-CDR (using ref clock only until locked)

- SSC on or off:

- Common for TX and RX, both TX's use same ref clk

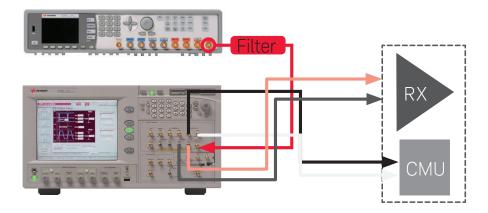

## Test Setup of a J-BERT

Test setup of a J-BERT with the 81150A for LF noise; the filtered signal from the 81150A is used as delay control input for the J-BERT.

An equivalent setup is valid for the ParBERT 81250A.

The N5990A test automation software supports PCIe 2.0 compliance testing and characterization with J-BERT and ParBERT configurations.

Figure 1. Test setup of a J-BERT with the 81150A for LF noise; the filtered signal from the 81150A is used as delay control input for the J-BERT. ISI and channel effects are merged into the signal path of the J-BERT by using the built-in trace 2.

# The PCle 2.0 Jitter Specification for Receiver Tests

Table 2. The PCIe 2.0 jitter specification for receiver tests

| Specifications and characteristics                     | Common reference clock architecture | Data clocked architecture |

|--------------------------------------------------------|-------------------------------------|---------------------------|

| Impedance                                              | 50 Ω                                |                           |

| Low frequency pass band                                | 0.01 – 1.5 MHz                      |                           |

| High frequency pass band                               | 1.5 – 100 MHz                       |                           |

| LF   <sub>2</sub> /   HF   <sub>2</sub> <sup>1,2</sup> | 4.2 / 3.8 ± 10%                     | 8.0 / 4.2 ± 10%           |

| Total insertion loss <sup>2,3</sup>                    | 21.4 ± 1 dB                         | 21.9 ± 1 dB               |

| Max. input voltage                                     | 10 V <sub>pp</sub>                  |                           |

| Input connector                                        | BNC (female)                        |                           |

| Output connector                                       | SMA (female)                        |                           |

| Operating temperature range                            | 0 – 55 °C                           |                           |

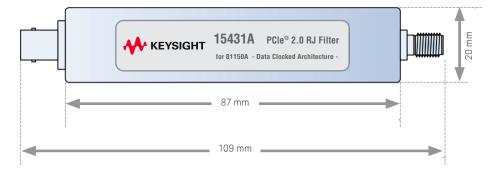

| Mech. dimensions (L x W x H)                           | 109 x 20 x 20 mm                    |                           |

| Weight                                                 | 71 g                                |                           |

<sup>1.</sup> Lp norm ||X||p yields rms value of X for p = 2 at +25 °C ± 5 °C ambient temperature 2. With 81150A as Gaussian noise source, crest factor = 7

Figure 2. 15431A dimensions

## Setting the correct output amplitude on the 81150A

For the reference clock filter the total rms jitter is  $(4.2^2 + 3.4^2)\frac{1}{2} = 5.4$  ps. The sensitivity of the J-BERT delay control input is specified with 400ps/V. Thus the filter's output voltage must be  $5.4/400 = 0.0135 \, V_{RMS}$  or  $13.5 \, mV_{RMS}$ . With an insertion loss of 21.4dB for the filter, the appropriate 81150A output voltage is 159 mVrms. The equivalent calculation for the data clocked filter with a total RMS jitter of 9 ps and 21.9 dB insertion loss yields 280 mV<sub>pMs</sub>.

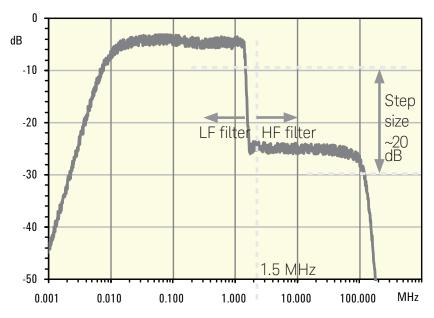

Figure 3. RJ filter noise spectrum for common reference clock architecture with 81150A as noise source

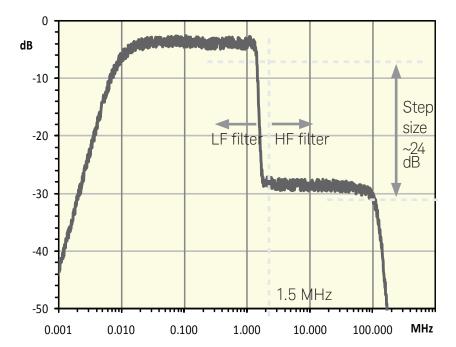

Figure 4. RJ-filter noise spectrum for data clocked architecture with 81150A

Jitter is separated into two bins:

LF: 0.01 - 1.5M Hz step BPF  $LF-RJ_{RMS} = 4.2 ps$

HF: 1.5 MHz step HPF and 100 MHz edge filtering  $HF-RJ_{RMS} = 3.4 ps$

15431 RCA-filter specification:  $|\text{LF-RJ/HF-RJ}|_{\text{RMS}} = 1.23 \pm 10\%$ Total insertion loss: 21.4 ±1 dB

Jitter is separated into two bins:

LF: 0.01 - 1.5 MHz step BPF  $LF-RJ_{RMS} = 8.0 ps$

HF: 1.5 MHz step HPF and 100 MHz edge filtering  $HF-RJ_{RMS} = 4.2 ps$

15431 DCA-filter specification:  $|LF-RJ/HF-RJ|_{RMS} = 1.9 \pm 10\%$

Total insertion loss: 21.9 ±1 dB

# Related Keysight Literature

Table 3. Related literature

| Publication title                                                   | Pub number  |

|---------------------------------------------------------------------|-------------|

| Keysight 81150A Pulse Function Arbitrary Noise Generator Data Sheet | 5989-6433EN |

| Keysight J-BERT N4903A High-Performance Serial BERT                 | 5989-2899EN |

| Test Automation Software Platform N5990A                            | 5989-5483EN |

| Keysight ParBERT 81250, Parallel Bit Error Ratio Tester             | 5968-9188E  |

### **Evolving Since 1939**

Our unique combination of hardware, software, services, and people can help you reach your next breakthrough. We are unlocking the future of technology. From Hewlett-Packard to Agilent to Keysight.

#### myKeysight

#### myKeysight

#### www.keysight.com/find/mykeysight

A personalized view into the information most relevant to you.

#### http://www.keysight.com/find/emt\_product\_registration

Register your products to get up-to-date product information and find warranty information.

KEYSIGHT SERVICES Accelerate Technology Adoption. Lower costs.

#### **Keysight Services**

#### www.keysight.com/find/service

Keysight Services can help from acquisition to renewal across your instrument's lifecycle. Our comprehensive service offerings—onestop calibration, repair, asset management, technology refresh, consulting, training and more—helps you improve product quality and lower costs.

### Keysight Assurance Plans

#### www.keysight.com/find/AssurancePlans

Up to ten years of protection and no budgetary surprises to ensure your instruments are operating to specification, so you can rely on accurate measurements.

#### Keysight Channel Partners

#### www.keysight.com/find/channelpartners

Get the best of both worlds: Keysight's measurement expertise and product breadth, combined with channel partner convenience.

$\mbox{PCI-SIG@}, \mbox{PCIe}\mbox{@}$  and  $\mbox{PCI Express}\mbox{@}$  are U.S. registered trademarks and/or service marks of PCI-SIG.

www.keysight.com/find/PCle\_receiver\_test

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

#### Americas

Canada (877) 894 4414 Brazil 55 11 3351 7010 Mexico 001 800 254 2440 United States (800) 829 4444

#### Asia Pacific

Australia 1 800 629 485 800 810 0189 China Hong Kong 800 938 693 India 1 800 11 2626 0120 (421) 345 Japan 080 769 0800 Korea 1 800 888 848 Malaysia Singapore 1 800 375 8100 0800 047 866 Taiwan Other AP Countries (65) 6375 8100

#### Europe & Middle East

For other unlisted countries: www.keysight.com/find/contactus (BP-9-7-17)

Opt. 3 (IT)

0800 0260637

United Kingdom

www.keysight.com/go/quality

Keysight Technologies, Inc. DEKRA Certified ISO 9001:2015 Quality Management System